C’è una grossa differenza tra un impulso e un progetto

ELETTRONICA DIGITALE

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

FAMIGLIE LOGICHE COMUNI

Famiglia logica TTL

La famiglia logica TTL (Transistor Transistor Logic) utilizza

solamente transistor BJT.

Il circuito base della logica TTL, indipendentemente dalla sotto-

-famiglia, è la porta NAND.

nella sottostante figura è disegnata la NAND gate.

La NAND TTL è costituita da uno stadio d’ingresso rappresentato da un BJT multiemettitore e

dai diodi presenti su tutte le linee di input, da un transistor TR2, chiamato phase splitter, e

da uno stadio di uscita a totem pole.

Il transistor TR1 ha tanti emettitori quanti sono gli ingressi; i diodi D1 D2 e D3 servono a

impedire che eventuali picchi di tensione negativi possano danneggiare il circuito.

La configurazione dello stadio di uscita si definisce di tipo totem pole.

I vantaggi e gli svantaggi di uno stadio di uscita con configurazione a totem pole sono i

seguenti:

•

un elevato fan-out;

•

un basso assorbimento di potenza dall’alimentatore; lo stadio di uscita potrebbe essere

costituito soltanto dalla R3 e dal TR4, infatti il TR3 e il D4 non sono strettamente

indispensabili, ma servono a limitare il valore della corrente assorbita ICsat dal TR4

quando è in saturazione; la potenza dissipata dalla porta logica diventa così molto bassa;

•

una elevata velocità di commutazione; quando l’uscita è nello stato alto, la relativa

resistenza Rout è molto bassa (circa 10 Ω e pertanto un carico capacitivo), pilotato dalla

porta, potrà caricarsi in un tempo brevissimo, consentendo al segnale di uscita di avere

tempi di salita estremamente rapidi; ricordiamo, infatti, che la carica di un condensatore

dura 4-5 volte la costante di tempo τ = RC, che è molto bassa perché è piccola la

R = Rout.

L’inconveniente principale del totem pole è costituito dal fatto che quando l’uscita passa

dallo stato basso a quello alto, per un breve intervallo di tempo, TR3 e TR4 sono contempo-

-raneamente in conduzione.

TR4 impiega un tempo maggiore per andare in interdizione rispetto al tempo necessario a

TR3 per andare in saturazione, quindi per un certo intervallo di tempo i due BJT sono

simultaneamente in conduzione.

La conduzione impulsiva e contemporanea dei due transistor di uscita comporta un conside-

-revole assorbimento di corrente dall’alimentatore (circa 10 volte superiore al valore

normale) e la generazione di impulsi.

Questo problema può essere limitato inserendo tra l’alimentazione e massa un condensa-

-tore, chiamato di bypass, con il compito di cortocircuitare gli impulsi di tensione.

Il condensatore (di tipo ceramico) deve essere collegato tra l’alimentazione e massa nelle

immediate vicinanze dell’integrato e deve avere un valore compreso tra 0,01 μF e 0,1 μF.

Sottofamiglie

La famiglia TTL è suddivisa in varie sottofamiglie che si differenziano tra loro per l’assorbi-

-mento di potenza e la velocità; la tensione di alimentazione resta invariata per tutti a

+5 V; le sottofamiglie più diffuse sono le seguenti:

•

TTL Standard;

•

TTL Schottky (S)

•

TTL Low-Power Schottky (LS);

•

TTL Fast;

•

TTL Advanced Schottky (AS);

•

TTL Advanced Low-Power Schottky (ALS)

TTL con stadio di uscita a open collector

Le porte logiche con uscita a open collector (in

figura a lato è riportato un esempio di NAND) sono

così chiamate perché il collettore del transistor di

uscita TR3 non è collegato all’alimentazione.

Il funzionamento della porta logica, analogo alla

NAND con uscita a totem pole, è garantito dal

collegamento di una resistenza di pull-up, esterna

all’integrato, da collegare all’alimentazione.

La resistenza di pullup deve essere dimensionata

in modo tale che la corrente di pozzo assorbita

dall’uscita della porta a livello basso non superi

il valore di .

Le porte logiche con stadio di uscita di tipo open

collector sono sempre più lente delle rispettive porte con stadio di uscita totem pole.

Infatti, essendo la notevolmente più grande della dello stadio a totem pole,

il carico capacitivo pilotato si carica attraverso la in un tempo molto più elevato.

Le porte logiche con stadio di uscita a open collector vengono utilizzate laddove la

velocità non costituisce un problema critico.

NAND TTL con stadio di

uscita open-collector

Famiglia logica CMOS

La famiglia logica CMOS è formata da una rete di transistor pMOS (rete di pull-up) e

da una rete di transistor nMOS (rete di pull-down).

La rete di pull-up serve per collegare l’uscita alla tensione di alime-

-ntazione, mentre la rete di pull-down collega l’uscita a massa.

La logica CMOS ha come porta fondamentale l’inverter

mostrato a lato.

I gate dei due MOS sono collegati tra loro e costituiscono l’ingresso

dell’inverter, mentre i due drain, anch’essi collegati tra loro, rap-

-presentano il terminale di uscita.

I due MOS sono alternativamente uno on e l’altro off.

Infatti con ingresso alto pMOS è interdetto e nMOS è in conduzione

portando l’uscita a massa.

Viceversa con ingrasso basso, pMOS collega l’uscita con l’alimentazione, nMOS invece è

interdetto.

Dall’ingresso del gate il MOS si presenta come una resistenza di

in parallelo ad una

capacità di 5 pF.

Se il MOS è on il canale ha una resistenza di circa 200 Ω, se invece è off si può ritenere

che la resistenza del canale sia infinita.

Per ogni transistor si definisce il rapporto , dove W è la larghezza del canale e L

la lunghezza.

Affinché la caratteristica dell’inverter sia simmetrica è necessario che risulti

dove μ è la mobilità dei portatori.

Una caratteristica di trasferimento simmetrica comporta tempi di salita e discesa uguali.

In tal modo pMOS e nMOS hanno la stessa capacità di pilotare carichi.

Normalmente il valore del rapporto tra le mobilità è compreso nel seguente intervallo

.

Spesso i costruttori assegnano al rapporto il valore di 2 allo scopo di ridurre l’area di silicio

occupata e la capacità d’ingresso.

Tuttavia questa scelta comporta la perdita della simmetria nella risposta dei tempi.

Il tempo di salita dipende dal rapporto del p MOS, mentre il tempo di discesa

è funzione del rapporto di n MOS.

Il ritardo di propagazione può essere ridotto:

•

diminuendo la capacità di carico che vuol dire diminuire la capacità di diffusione interna

e il fan-out;

•

diminuendo il rapporto R che comporta un aumento della capacità di diffusione e del

fan-out della porta precedente;

•

aumentando la che comporta un aumento della potenza dissipata.

Porte logiche open-drain

L’open drain, analogo all’open collector, è una tecnica circuitale che consente il collega-

-mento in parallelo tra le uscite delle porte logiche quando devono confluire tutte simu-

-ltaneamente sullo stesso bus.

Non è possibile collegare in parallelo due porte CMOS perché un pMOS e un nMOS

entrambi in conduzione farebbero circolare una corrente molto elevata e la tensione di

uscita potrebbe non corrispondere a un livello logico canonico.

Infatti i CMOS sono programmati per non far passare corrente in entrambi gli stati logici.

Le porte open-drain sono prive del pMOS pertanto necessitano di una resistenza esterna

di pull-up opportunamente progettata per avere una tensione a livello basso inferiore alla

tensione di soglia.

La resistenza di pull-up comporta un peggioramento delle caratteristiche dinamiche della

porta logica.

La porta open-drain è connessa a massa nello stato logico 0, in tal caso è percorsa da

una corrente di sink, mentre nello stato logico 1 è in alta impedenza.

Caratteristiche

In genere i CMOS presentano le seguenti caratteristiche:

•

sono molto robusti;

•

hanno una densità di integrazione superiore a quella dei TTL e degli ECL; sono utilizzati

negli integrati SSI e MSI; per gli integrati VLSI è preferibile la tecnologia nMOS perché

consente una maggiore densità;

•

hanno un alto margine di rumore;

•

generano rumore durante le transizioni;

•

hanno una escursione quasi totale della tensione di uscita, da massa alla tensione

di alimentazione;

•

non assorbono potenza statica; la potenza dinamica invece non è trascurabile e

comunque aumenta considerevolmente con la frequenza delle commutazioni;

•

hanno differenti tempi di ritardo tra rete di pull-up e pulldown; il ritardo di propaga-

-zione è leggermente superiore ai TTL;

•

la capacità d’ingresso dipende sia da pMOS sia da nMOS;

•

NAND e NOR sono veloci, mentre XOR e MUX sono lenti;

•

il fan-out è elevato, la limitazione è costituita dalle capacità parassite degli ingressi che

si sommano e quindi tendono a rallentare l’uscita della porta pilotante.

•

hanno una elevata sensibilità alle scariche elettrostatiche, per tale motivo sono

provvisti, di un circuito di protezione ESD;

•

sono soggetti al fenomeno del latch-up;

•

il processo di fabbricazione è più complesso rispetto alla tecnologia pMOS e nMOS;

•

hanno una elevata impedenza d’ingresso e una bassa impedenza di uscita.

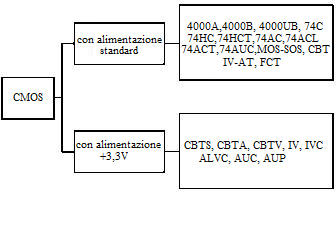

Sottofamiglie

Le famiglie CMOS con VCC = +5 V sono

riportate nella figura a destra.

Serie 4000A

La serie 4000A è la prima famiglia logica

immessa sul mercato, quindi è la più

vecchia e la più economica.

La tensione e la corrente di uscita dipendono

dalle condizioni di funzionamento della porta stessa, ossia da quali MOS sono in

conduzione.

La caratteristica di trasferimento è lontana da quella ideale, i tempi di propagazione

basso-alto e alto-basso sono diversi e in generale la velocità di commutazione è bassa.

Serie 4000B

La serie 4000B è stata ottenuta dalla 4000 aggiungendo semplicemente due stadi

invertitori (buffer) tra lo stadio che svolge la funzione logica e l’uscita.

Con l’introduzione di questi buffer migliorano i seguenti parametri:

•

la caratteristica di trasferimento risulta molto prossima a quella ideale;

•

i tempi di salita e di discesa sono più piccoli e uguali tra loro;

•

il ritardo di propagazione è maggiore rispetto alla serie 4000A.

La tensione di alimentazione può variare da 3 a 18 V, ma le case costruttrici raccoman-

-dano un funzionamento con una tensione compresa tra i 3 e i 15 V.

Serie 74HC

Utilizzando una tecnologia particolare è stato possibile ottenere una serie ad alta

velocità (HCMOS, High speed CMOS).

I tempi di ritardo sono circa dieci volte più piccoli della serie 74C.

Gli integrati di questa famiglia sono inoltre provvisti di una protezione contro le scariche

elettrostatiche e contro la distruzione dovuta a sovratensioni (fenomeno di latch-up).

I componenti della famiglia logica ad alta velocità 74HC sono compatibili, sia per la

disposizione dei piedini che per le funzioni implementate, con i corrispondenti compo-

-nenti della famiglia TTL LS ma con il vantaggio di offrire un significativo risparmio di

potenza che è da 5 a 6 ordini di grandezza inferiori.

Le caratteristiche sono le seguenti:

•

ritardo di propagazione comparabile con la serie TTL LS;

•

frequenza massima di funzionamento pari a 50 MHz;

•

capacità di erogare e/o assorbire correnti 10 volte più grandi della serie 4000B;

•

tensione di alimentazione compresa tra 2 e 6 V;

•

potenza dissipata di 2,5 nW in condizioni statiche e di 1,7 mW in condizioni dinamiche

(è stata presa come riferimento una porta NAND).

Serie 74AC e 74ACL

Si tratta di una generazione di integrati CMOS che possiedono tempi di ritardo e di

commutazione comparabili alla TTL ALS, ma con un basso assorbimento di potenza,

tipico della tecnologia unipolare e con una differente disposizione dei piedini.

La posizione dell’alimentazione e della massa alle estremità rende massima l’induttanza

dovuta al contenitore e ciò genera impulsi di rumore che possono provocare la perdita

dei dati.

I pin della massa e dell’alimentazione sono posti al centro del contenitore.

Riassumendo le principali caratteristiche sono:

•

ritardo di propagazione paragonabile a TTL ALS;

•

uscita di tipo bufferizzato;

•

tensione di alimentazione VDD = 2-6 V;

•

capacità di pilotare una corrente di circa 24 mA;

•

riduzione del rumore della tensione di uscita.

Famiglia logica BiCMOS

La famiglia logica BiCMOS (Bipolar CMOS), è stata ottenuta combinando la tecnologia

CMOS con la tecnica bipolare ottenendo i seguenti vantaggi:

•

una elevata impedenza d’ingresso;

•

una flessibilità progettuale;

•

una elevata scala di integrazione;

•

un assorbimento di potenza statica teoricamente nulla;

•

una più elevata capacità di pilotare grandi carichi capacitivi grazie allo stadio di

uscita a BJT.

Le applicazioni tipiche di questa famiglia logica sono:

•

pilotaggio di bus;

•

buffer di ingresso/uscita;

•

pilotaggio di grandi carichi capacitivi in tempi brevi.

•

Porta NOT

A destra è disegnato lo schema di

principio di una porta logica NOT, in

tecnologia BiCMOS, ottenuta con uno

stadio d’ingresso (phase-splitter) CMOS

e con uno di uscita a push-pull (totem

pole), tipico della struttura TTL.

Uno stadio d’ingresso a CMOS consente di

avere una impedenza d’ingresso molto

elevata; uno stadio di uscita a BJT

permette una maggiore capacità di

erogare correnti più elevate ai carichi.

Famiglia logica ECL

La ECL (Emitter Coupled Logic, logica ad accoppiamento di emettitore) è una famiglia

logica non saturata, concepita per avere elevate prestazioni. Introdotta nel 1961 dalla

General Electric è stata successivamente perfezionata dalla Motorola con le serie 10K e

100K attualmente ancora in commercio perché presentano un ritardo di propagazione

inferiore a 1 ns, circa 500 ps.

Gli svantaggi, costituiti essenzialmente dall’elevato assorbimento di potenza statica,

dal basso margine di rumore, dalle tensioni negative di alimentazione e dei livelli

logici, la rendono poco utilizzabile in quasi tutte le applicazioni.

Le sue caratteristiche si possono così riassumere:

•

logica non saturata;

•

ogni porta è dotata di due uscite (diretta e complementata);

•

ritardo di propagazione dell’ordine dei ps;

•

swing di tensione ridotto, inferiore a 1 V, circa 0,8 V;

•

bassa impedenza di uscita, di conseguenza elevato fan-out;

•

elevato assorbimento di potenza statica;

•

parametro PDP paragonabile ai CMOS;

•

struttura delle porte logiche complessa, processo di fabbricazione costoso;

•

bassa scala di integrazione;

•

necessità di traslatori di livello nell’accoppiamento con altre logiche;

•

sensibilità ai disturbi introdotti dalla linea di alimentazione.

La tecnologia ECL è utilizzata in applicazioni particolari, ad esempio come interfaccia di

ricetrasmissione a fibra ottica nelle reti Gigabit Ethernet e nelle reti ATM (Asynchronous

Transfer Mode).

La tecnologia di costruzione è basata sul transistor BJT che, a differenza di quanto

avviene nella TTL, non lavora in saturazione e interdizione ma in zona attiva, passando

da uno stato di forte a uno di debole conduzione.

Schema generale di un gate in

tecnologia Bipolar CMOS.

Interfacciamento tra famiglie logiche

Nella realizzazione dei sistemi digitali sono spesso utilizzate porte logiche di tecnologie

diverse.

Una scelta ibrida dei componenti ha l’unico scopo di ottenere il massimo rendimento al

meglio dalle caratteristiche di ciascuna famiglia logica.

Nasce però il problema di rendere compatibili tra loro i diversi componenti impiegati.

Esempi tipici di interfacciamento si hanno quando:

•

i sistemi digitali vengono realizzati con i CMOS per l’elevata integrazione di questa

famiglia e impiegano TTL come componenti periferici perché sono in grado di pilotare

carichi elevati;

•

i sistemi digitali sono implementati con i TTL, che lavorano con una frequenza

relativamente bassa, e con gli ECL che lavorano a frequenze molto più elevate.

Per poter connettere due famiglie logiche diverse è necessario verificare la reciproca

compatibilità.

L’interfacciamento è l’operazione che permette a due o a più componenti di funzionare

insieme in modo corretto, di essere cioè compatibili per quanto riguarda i livelli delle

tensioni, delle correnti e dei tempi di ritardo.

Se le famiglie logiche non sono compatibili tra loro, è necessario inserire un circuito

di interfaccia tra l’uscita della porta pilotante e l’ingresso della porta pilotata.

Indicando con 1 la porta pilotante e con 2 la porta pilotata, la compatibilità delle tensioni

si ha quando sono verificate le seguenti condizioni:

•

con uscita a livello logico alto;

•

con uscita a livello logico basso.

La compatibilità delle correnti si ha quando sono verificate le seguenti condizioni:

•

con uscita a livello logico alto;

•

con uscita a livello logico basso.

Il rapporto tra le correnti determina il fan-out della porta pilotante.

Il fan-out a livello alto deve essere calcolato con il rapporto e a livello basso

.

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor