Mentre cerchiamo di capire, il tempo passa e la vita con lui

ELETTRONICA DIGITALE

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

CIRCUITI INTEGRATI COMBINATORI- ALU

Definizioni

Esiste in commercio, a disposizione dei progettisti, una vasta

gamma di circuiti integrati in cui sono già implementate funzioni

combinatorie dalle più semplici alle più complesse.

L’utilizzo dei circuiti integrati, contenenti reti combinatorie in

grado di svolgere determinate funzioni, porta a indubbi vantaggi

rispetto ad una realizzazione in logica sparsa, ovvero con singole

porte logiche.

Infatti il sistema digitale risulta complessivamente più semplice

e più economico sia perché utilizza un minor numero di integrati

sia per un minor numero di collegamenti.

È evidente inoltre che questo tipo di implementazione comporta un risparmio di tempo (si

pensi al tempo necessario per la progettazione) e una maggiore facilità nella ricerca di un

eventuale guasto.

Al progettista viene quindi richiesta la capacità di saper scegliere dal Data Book gli integrati

idonei alla realizzazione del suo sistema.

La progettazione con componenti discreti è limitata a quei pochi casi in cui è necessario

creare un’interfaccia tra i diversi integrati oppure adattare alle specifiche esigenze l’integrato

scelto.

Di seguito viene descritto il funzionamento degli integrati MSI (Medium Scale Integration)

più significativi che vengono utilizzati frequentemente nei sistemi digitali: codificatori,

decodificatori, multiplexer, demultiplexer, convertitori di codice, comparatori, generatori/ri-

-velatori di parità.

Codificatore (encoder)

Il codificatore (encoder) è un circuito combinatorio che genera sull’uscita

un’informazione, codificata in un codice binario, corrispondente a un dato presente

su una linea d’ingresso. Il codificatore è un circuito che trasforma una informazione,

presente in ingresso e scritta in un codice orientato all’uomo, in un’altra, scritta in un

codice orientato alla macchina.

Il dato da codificare può essere costituito da una cifra decimale, ottale, esadecimale, da un

carattere alfabetico o speciale, ecc.; il dato, codificato in uscita in un codice binario, cor-

-risponde alla cifra, alla lettera o al simbolo.

Nella sottostante figura è riportato il simbolo logico di un codificatore da 8 a 3 linee mentre

a lato si trova la corrispettiva tavola della verità relativa alla funzione.

I0

I1

I2

I3

I4

I5

I6

I7

A0

A1

A2

1

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

0

0

0

1

0

1

1

0

0

0

0

0

0

0

0

1

1

1

0

Simbolo logico e tabella della funzione di un codificatore da 8 a 3

Un codificatore ha n linee di uscita e 2^n linee d’ingresso. Questo tipo di codificatore

presenta l’inconveniente di fornire un’uscita non valida se più ingressi sono attivati conte-

-mporaneamente.

Infatti dalla figura [b] si nota che gli ingressi devono essere attivi singolarmente.

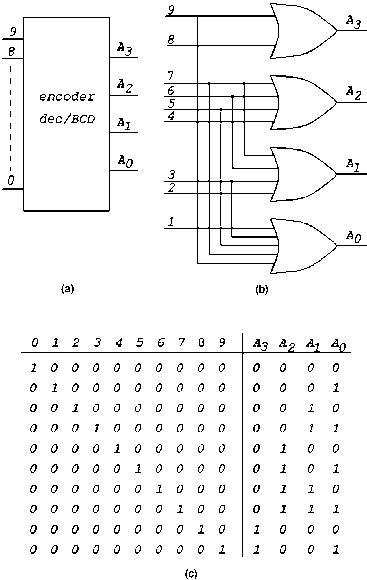

Un esempio è il codificatore decimale/BCD che converte un numero decimale in uno BCD.

Nelle figure [a] e la sottostante [b] sono riportati il simbolo logico e il circuito che imple-

-menta la relativa tabella [c].

Con riferimento a questa tabella, se le 10 linee d’ingresso possono essere attivate dai 10

tasti di una tastiera numerica, le 4 linee di uscita forniscono il numero decimale codificato

in BCD.

Ad esempio attivando la linea 7, il dato in uscita risulta A3 A2 A1 A0 = 0111.

Il circuito di figura (b) implementa il codificatore. Le uscite A sono attive secondo le

funzioni evidenziate a alto.:

[a]

[b]

A0 = 1 + 3 + 5 + 7 + 9

A1 = 2 + 3 + 6 + 7

A2 = 4 + 5 + 6 + 7

A3 = 8 + 9

Simbolo logico (a), circuito (b) e tabella

della verità (c) del codificatore decimale/BCD.

Codificatore con priorità (priority encoder)

Per superare l’inconveniente presente nel codificatore è stato realizzato il codificatore con

priorità nel quale, se vengono attivate simultaneamente più linee d’ingresso, sarà

codificato in uscita il dato presente sulla linea con maggiore priorità.

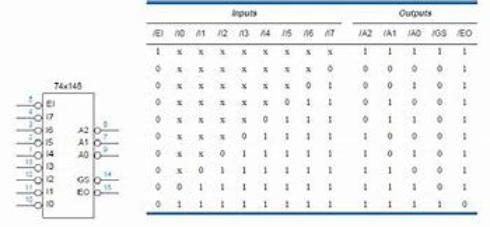

Un esempio di codificatore con priorità è l’integrato 74148 che codifica in BCD (8421) su

3 bit con priorità le 8 linee d’ingresso.

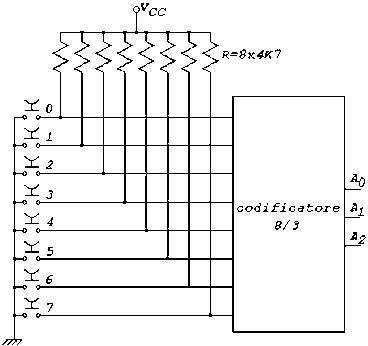

Una delle applicazioni del codificatore con priorità consiste nella codifica di una tastiera.

In figura a lato è riportato lo schema

circuitale per la realizzazione della codifica

dei pulsanti di una tastiera.

Ogni linea d’ingresso è connessa all’alimenta-

-zione tramite una resistenza di pull-up da

4,7 kΩ; quando viene digitato un tasto il

relativo ingresso del codificatore è collegato

a massa e in uscita si ha la codifica del cor-

-rispondente codice binario.

Se più tasti vengono digitati contemporane-

-amente in uscita si ha la codifica di un solo

tasto, quello con priorità maggiore.

Codifica dei pulsanti di una tastiera

Decodificatore (decoder)

Il decodificatore esegue un’operazione che consiste nel tradurre un dato, scritto in un

codice orientato alla macchina, per esempio in BCD, in un codice orientato all’uomo.

Il decodificatore svolge la funzione inversa a quella del codificatore.

Il circuito attiva una sola linea di uscita per ogni combinazione di bit (codice) presente

sulle linee d’ingresso.

Con n linee d’ingresso si possono avere mas-

-simo

uscite.

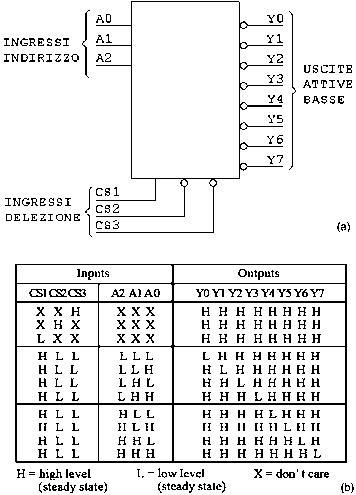

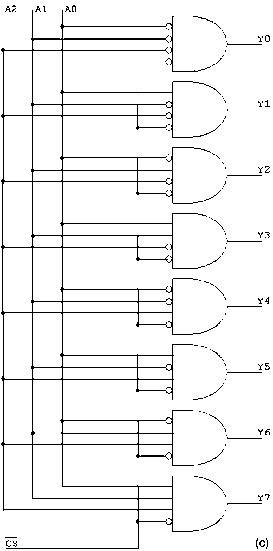

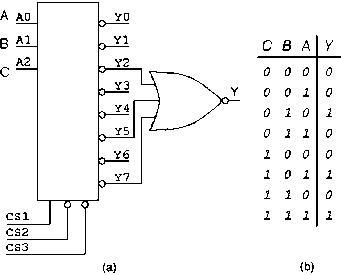

Nelle figure a lato (a) e ( c) sono disegnati il

simbolo logico ed il circuito, mentre nella

figura (b) è riportata la tabella della funzione

di un decoder da 3 a 8 linee, chiamato anche

1 di 8, ovvero una sola linea di uscita attiva

su 8.

Ogni configurazione delle variabili d’ingresso

attiva una sola porta AND, quindi una sola

uscita

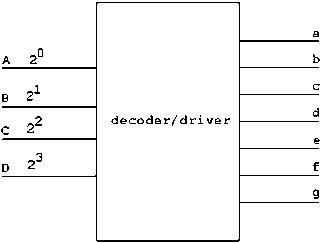

Decoder/driver per display a 7 segmenti

Il decoder/driver è un decodificatore particolare

che trasforma il dato d’ingresso, espresso nel

codice BCD, in segnali necessari a pilotare un

display a 7 segmenti, ovvero un componente

optoelettronico idoneo a visualizzare il dato.

Per ogni dato BCD posto in ingresso, vengono

attivate le linee di uscita in modo tale da

alimentare i segmenti del display così da visualiz-

-zare il numero decimale o esadecimale.

Un decoder/driver con molteplici funzioni è il

9368 della Fairchild.

Il 9368 è un integrato MSI appartenente alla

famiglia 9000 prodotta dalla Fairchild.

Simbolo logico di un decoder/driver per

display a 7 segmenti

Decoder come generatore di funzione

Un decoder può essere utilizzato anche per gene-

-rare una qualsiasi funzione combinatoria.

Si supponga di voler implementare la funzione

indicata nella tabella raffigurata a lato.

Per ottenere la funzione desiderata è sufficiente

collegare ad una porta NOR tutte le uscite cor-

-rispondenti ai mintermini veri della funzione,

che sono .

In figura (a) è illustrato il circuito.

Decoder (a) usato come generatore

della funzione indicata in tabella

Multiplexer

Il multiplexer (MUX) è un selettore dati e trasmettere

sull’unica linea di uscita il dato presente su uno dei

molti ingressi.

Un’applicazione tipica del multiplexer è quella di

smistare i dati provenienti da più sorgenti verso un

unico dispositivo di visualizzazione.

Il multiplexer è utile in moltissimi campi applicativi

come ad esempio la conversione parallelo/seriale dei

dati, la generazione di funzioni booleane, la genera-

-zione di forme d’onda, lo smistamento di più cifre su

un unico sistema di visualizzazione ecc.

Nella figura (a) a lato è disegnato l’equivalente mec-

-canico del multiplexer.

In generale un

multiplexer possiede una sola uscita, n linee di selezio-

-ne e

linee di ingresso per i dati.

Il simbolo logico è mostrato nella figura (b).

Per aumentare il numero degli ingressi di un multiplexer

si possono adottare almeno due strategie di collegame-

-nto di più integrati, in parallelo o in multilivello.

Un esempio di multiplexer è il 74150.

L’integrato è dotato di un ingresso G (strobe input)

attivo basso, che abilita il chip al funzionamento, e 16 ingressi dati.

Se sui quattro ingressi di selezione A B C D si invia una delle sedici possibili configurazioni,

sull’uscita W appare il dato negato presente sull’ingresso selezionato, da E0 a E15

Equivalente meccanico di un multiplexer (a)

e simbolo logico di un multiplexer a 4 ingressi (b)

Multiplexer come generatore di funzione

Il MUX può essere utilizzato anche come generatore di una funzione booleana combinatoria

purché scritta sotto forma di somma di prodotti.

Con tale procedura si ottengono spesso alcuni vantaggi, quali un minor numero di integrati

utilizzati rispetto a una implementazione con porte logiche e un minor tempo per la fase

teorica di progettazione.

Esempio

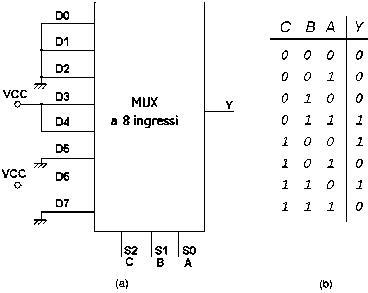

Implementare la funzione booleana combinatoria descritta nella sottostante tabella (b),

utilizzando un MUX con otto ingressi dati e

tre ingressi di selezione.

La funzione ha tre variabili indipendenti

(A,B,C) che vanno inviate sugli ingressi

data selector (S0, S1, S2) mentre a

ciascun ingresso dati si collega perma-

-nentemente la massa o l’alimentazione

a seconda del valore assunto dalla funzio-

-ne in corrispondenza di quella data

configurazione.

In figura è riportata la relativa realizza-

-zione circuitale.

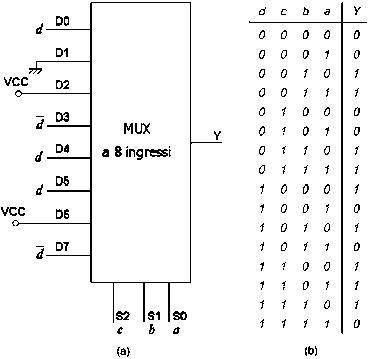

Esempio

Implementare una funzione combinatoria

con quattro variabili indipendenti

utilizzando un MUX con tre ingressi di

selezione. La funzione è riportata nella

tabella di figura (b) mentre in fig. 16.32a è

disegnato il circuito.

Le tre variabili di peso inferiore (a, b, c)

devono essere poste sugli ingressi di sele-

-zione.

La tabella deve essere divisa in due parti:

la prima metà con d = 0 e la seconda con

d = 1.

Le combinazioni differenti per la sola

variabile d devono essere prese in consider-

-azione a coppie per poter assegnare a ogni

ingresso dati il valore di a seconda

della coppia di configurazioni.

Multiplexer a 8 ingressi (a) che implementa la funzione

combinatoria a 3 variabili indicata in tabella

Multiplexer a 8 ingressi (a) che implementa la

funzione combinatoria a 3 variabili indicata in tabella (b).

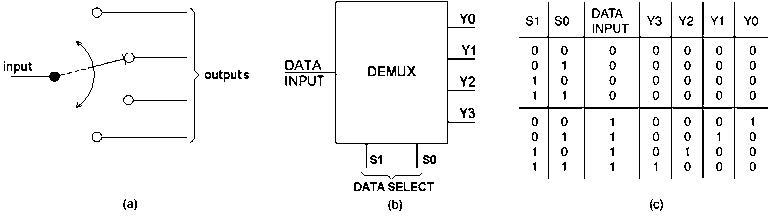

Demultiplexer

Il demultiplexer (DEMUX) trasmette su una linea di uscita selezionata il dato presente

sull’unico terminale d’ingresso.

Il demultiplexer svolge la funzione opposta a quella del multiplexer; nella sottostante

figura (a) è riportato l’equivalente meccanico:

il commutatore ruotando entra in contatto con i terminali fissi e mette in comunicazione la

linea di uscita selezionata con l’ingresso.

Un demultiplexer possiede un ingresso dati, n linee di selezione e

linee di uscita.

In figura ( c) è riportata la tabella di verità e in figura (b) il simbolo logico.

Il demultiplexer ha la stessa struttura di un decoder; infatti con riferimento alla

tabella di verità del decoder , si nota che se gli ingressi CS2 e CS3 sono disattivi (cioè a

livello basso) allora gli ingressi A0, A1, A2 sono utilizzati come ingressi di selezione.

Il dato presente sull’uscita selezionata è lo stesso, ma negato, presente sull’ingresso

dati CS1.

Per tale motivo sui data sheet si trovano integrati indicati come decoder/demultiplexer.

Per aumentare il numero delle uscite si possono adottare almeno due strategie di collega-

-mento di più integrati, in parallelo o in multilivello.

L’integrato 74154 è un decoder/demultiplexer da 4 a 16 linee. Per l’utilizzo come

demulplexer, si pone stabilmente a massa G1 e si usa G2 come ingresso dati.

Se sugli ingressi D, C, B, A si pone la configurazione LHLH, tutte le linee di uscita saranno

disabilitate (livello H) mentre sull’uscita 5 si avrà il dato presente su G2.

Infatti se il dato in ingresso è L, il chip è abilitato al funzionamento, la linea 5 è attiva

(livello L) mentre se il dato è H, il chip è disabilitato, sulla linea 5 vi sarà un livello H.

Equivalente meccanico (a), simbolo logico (b) e tabella della funzione (c) di un demultiplexer a 4 uscite.

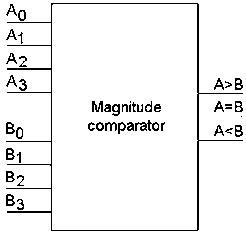

Comparatore

Il comparatore è un circuito combinatorio che confronta due dati binari e identifica con le

sue tre uscite le relazioni di uguaglianza, minoranza e maggioranza.

Il comparatore più semplice, in quanto segnala solo

l’uguaglianza, è la porta XNOR che pone bassa l’uscita

se i due ingressi sono uguali tra loro.

In figura a lato vi è il simbolo logico.

Simbolo logico di un comparatore a 4 bit.

Il 7485 è un comparatore che confronta due numeri

binari a 4 bit.

L’integrato è dotato di 8 ingressi dati A0, A1, A2, A3 e

B0, B1, B2, B3 corrispondenti alle due parole di 4 bit

da confrontare e di 3 cascading inputs (A > B, A = B,

A > B) che lo rendono flessibile nel suo utilizzo perché

si possono collegare in cascata più componenti per

realizzare comparatori di parole più lunghe di 4 bit.

Generatore/rivelatore di parità

Il generatore/rivelatore di parità è un circuito combinatorio che genera un bit di parità da

trasmettere insieme al dato e usato in ricezione rileva la presenza di un eventuale errore

nell’informazione. Gli integrati esistenti in commercio possono lavorare con la parità

o la parità dispari.

Il 74180 è uno dei più noti generatori/rivelatori di parità per dati a 8 bit.

Convertitore di codice

I convertitori di codice sono circuiti che consentono di convertire il codice con cui è

rappresentato un dato.

Ad esempio un dato numerico rappresentato in BCD deve

essere

convertito in un altro codice quando si esegue un’operazione di sottrazione.

Viceversa, ottenuto il risultato il dato deve essere riportato in BCD. Questi circuiti

combinatori possono essere implementati con varie tecniche:

• con MUX o decoder;

• con memorie ROM;

• con integrati standard;

• in logica sparsa

Convertitori implementati con MUX o decoder

L’operazione di conversione da un codice all’altro è una funzione booleana di tipo combina-

-torio e pertanto può essere realizzata con un multiplexer o un decoder utilizzati come

generatori di funzione.

In questo caso è necessario seguire la procedura per la progettazione della rete

combinatoria.

Convertitori implementati con memorie ROM

Nel caso di funzioni piuttosto complesse i circuiti vengono integrati in memorie di

tipo ROM.

Il dato da convertire è mandato in ingresso sulle linee di indirizzo al quale corrisponde lo

stesso dato ma espresso in un altro codice.

In questo caso non è richiesta alcuna progettazione ma solo la conoscenza delle funzioni

dell’integrato.

Convertitori implementati con integrati standard

Esistono in commercio alcuni integrati standard che eseguono solo alcune conversioni.

L’integrato 74184 è un convertitore da BCD a binario per numeri da 0 a 39.

Svolge inoltre anche la conversione del dato in complemento a 9 e a 10, ovviamente in

formato BCD.

Il 74185 è stato progettato per convertire da binario a BCD.

L’integrato MSI è a 6 bit per cui converte i numeri da 0 a 63.

Circuiti aritmetici

In commercio ci sono vari integrati che svolgono operazioni aritmetiche:

i sommatori e l’ALU.

I sommatori sono circuiti combinatori che elaborano segnali digitali secondo le leggi

dell’aritmetica binaria.

I sommatori possono essere di due tipi: paralleli e seriali.

La somma tra due numeri binari, per

esempio si esegue con le stesse regole dell’algebra numerica.

L’operazione ha inizio dalla colonna delle cifre meno significative, colonna 0, fino a quelle

più significative.

Durante l’operazione di somma si possono generare dei riporti che vanno sommati alla

colonna successiva. Soltanto nella prima colonna si sommano due soli bit.

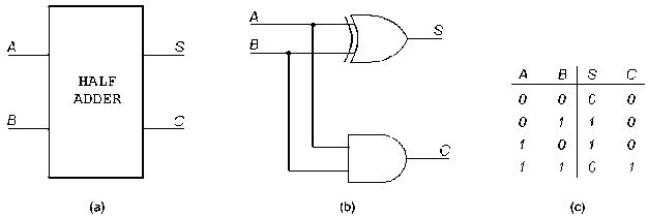

Semisommatore (half adder)

Il circuito che esegue la somma di due bit si definisce semisommatore (half adder) il

cui simbolo logico è rappresentato nela sottostante figura (a)

Nella tabella di verità (figura c) vi sono due uscite: la somma S e il riporto C (carry).

Il circuito di figura (b) è costituito da una porta AND per il riporto e da una XOR riguar-

-dante la somma.

Simbolo logico (a), circuito (b) e tabella della verità (c) del semisommatore (Half Adder)

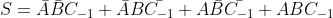

Sommatore (full adder)

Il sommatore completo (full adder) o semplicemente sommatore è un circuito combina-

-torio che somma i bit ed il bit di riporto proveniente da una operazione precedente.

Il metodo classico per realizzare il

sommatore è quello di ricavare le funzioni

dalla tabella di verità (figura b) ed eventu-

-almente semplificare le funzioni (somme

e riporti) con le mappe di Karnaugh che

risultano essere:

Il pedice −1 sta a indicare che si tratta del

bit della colonna precedente. I circuiti

ricavati dalle funzioni sono riportati nelle

figure schematiche in figura (a).

Circuito per la generazione della somma e del

riporto (a) e relativa tabella della verità (b).

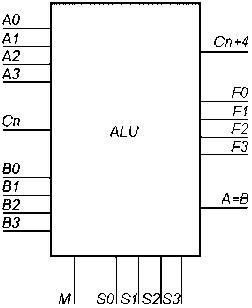

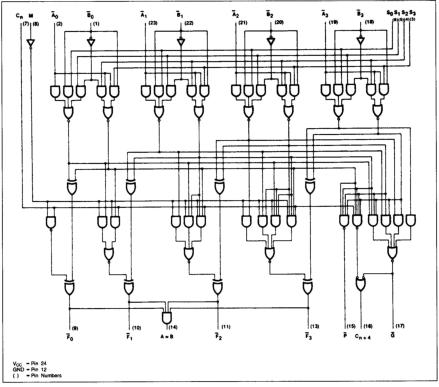

Unità logico-aritmetica (ALU)

L’ALU (Aritmetic Logic Unit) è un circuito in grado di svolgere operazioni aritmetiche e

logiche. In figura a lato è disegnato il simbolo logico di

una ALU che elabora dati a quattro bit.

I segnali d’ingresso e d’uscita possono essere raggruppati

nel seguente modo:

• , ingressi dei dati da elaborare;

• , ingressi per la selezione della funzione

da svolgere;

• M, ingresso di selezione del modo di funzionamento

aritmetico o logico.

• , ingresso del bit di riporto per eventuale espansione

del dato;

• , riporto di uscita;

•

, uscita che segnala l’uguaglianza tra i due dati binari;

• , bit di uscita della funzione.

Gli ingressi di selezione (M e Si) consentono di programmare l’integrato per svolgere le

seguenti operazioni matematiche:

• addizione;

• sottrazione

• spostamento del dato A di una posizione;

• condizione di uguaglianza;

• altre operazioni matematiche varie.

Le operazioni logiche invece sono le seguenti:

• XOR;

• AND, NAND, OR, NOR;

• comparazione;

• altre operazioni logiche.

Un esempio di ALU è il 74181 che rappresenta uno dei pochi integrati LSI in

tecnologia TTL.

L’integrato può lavorare sia in logica negativa sia in logica positiva

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor