Al fico l'acqua ed alla pera il vino

ELETTRONICA DIGITALE

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

PORTE LOGICHE

PORTE LOGICHE SPECIALI

Vi sono in commercio alcune porte logiche che hanno funzioni

particolari, si tratta dei buffer (driver e buffer/driver),

buffer/three-state, transceivers, porte logiche a trigger di

Schmitt e degli elementi di ritardo (delay elements).

Buffer e buffer/driver

I buffer sono porte logiche che hanno la funzione di separare e

rendere quindi possibile la connessione tra porte logiche, circuiti

digitali in generale, dispositivi e linee di bus.

Spesso i buffer sono anche driver perché sono in grado di erogare una corrente maggiore,

sono in pratica amplificatori di corrente. I buffer/driver possono essere invertenti e non

invertenti.

In figura a lato, sono illustrati i simboli logici.

Simboli logici dei buffer/driver

(a) invertente e (b) non invertente

Un esempio di buffer invertente è l’integrato

CMOS 4049 e un esempio non invertente è

l’integrato 4050

Buffer con uscita three-state

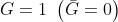

I buffer three-state sono dotati di un ingresso di controllo che può essere attivo a livello

basso o alto. In figura a lato sono rappresentati i simboli

logici.

Nell’integrato 74125 l’uscita è disabilitata quando

l’ingresso di controllo G è a livello alto; nell’integrato

74126 l’uscita è disabilitata quando G è basso.

Se l’uscita è disabilitata, la porta è in alta impedenza ovvero tra l’ingresso e l’uscita vi è

un’impedenza, infinita.

In questo caso è come se la porta logica non fosse più connessa al circuito.

La tecnica dell’uscita three-state è utilizzata in tutti gli integrati dei sistemi a bus, poiché il

dialogo tra i vari integrati deve avvenire in modo selettivo.

Comandando in modo opportuno gli ingressi di controllo dei componenti collegati al bus, è

possibile inviare dati da un’unica sorgente a uno o a più ricevitori escludendo gli altri; i

componenti disabilitati risultano non collegati al flusso di dati.

La tecnica di collegamento a bus con logica three-state consente una notevole riduzione

del numero di collegamenti da effettuare tra i singoli componenti ed evita che gli integrati

non interessati possano disturbare la trasmissione dei dati alterando il livello di tensione

presente sulle linee.

Transceivers

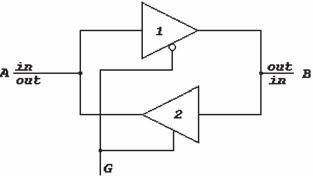

Con i buffer three-state si possono costruire porte bidirezionali, chiamate anche transceivers,

in grado di far transitare un dato nei due sensi

come mostra la figura a lato. Quando l’ingresso di

controllo G è a livello basso, è abilitata la porta

threestate 1, mentre il buffer 2 rende infinita

l’impedenza tra A e B: il dato può transitare da A

(ingresso) verso B (uscita).

Se l’ingresso G è a livello alto, il buffer 2 è abilitato

mentre è disabilitato il buffer 1: il dato transita da

B (ingresso) verso A (uscita).

Simboli logici dei buffer three-state:

(a) integrato 74125,

(b) integrato 74126

Porte logiche a trigger di Schmitt

Le porte logiche a trigger di Schmitt sono buffer che accettano in ingresso anche

segnali analogici e li trasformano in segnali digitali.

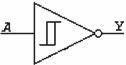

A lato è riportato il simbolo di un buffer invertente a trigger di

Schmitt tratto dal data sheet 7414 della Texas Instruments.

L’uscita del buffer commuta quando la tensione d’ingresso

raggiunge il valore di soglia superiore VT+; se la tensione d’ingresso diminuisce, la

commutazione dell’uscita si ha in corrispondenza di una tensione di soglia VT− (inferiore

alla VT+).

Valori della tensione d’ingresso leggermente differenti da VT+ e VT− assicurano alla porta

logica una certa immunità al rumore, cioè non consentono a eventuali tensioni spurie di far

commutare in modo indesiderato l’uscita. In tecnologia TTL, oltre ai buffer invertenti, vi

sono anche porte NAND a trigger di Schmitt, che fungono da funzione NAND e da

squadratori dei segnali analogici

Buffer invertente a Trigger di Schmitt

Elementi di ritardo

Gli elementi di ritardo (delay elements) sono porte logiche che ritardano il passaggio del

segnale posto in ingresso per un tempo ben definito e indicato dalle caratteristiche.

Servono a introdurre ritardi di tempo sulle linee laddove viene richiesto.

Un esempio di elemento di ritardo è l’integrato 74LS31 della Texas Instruments che

contiene elementi invertenti e non invertenti.

Porta di trasmissione (o interruttore bilaterale)

La porta di trasmissione (o interruttore bilaterale), implementata solo in tecnologia

CMOS e senza un corrispondente in tecnologia TTL e ECL, è un vero e proprio interruttore

unipolare comandato da una tensione di controllo.

Nella figura a lato è mostrata la configurazione fonda-

-mentale che consiste in un transistor NMOS in parallelo a

uno PMOS.

Tenendo presente che NMOS presenta un comportamento

da interruttore ideale per lo 0 logico e PMOS ideale per

1 logico, quando entrambi i MOS sono

aperti; con i MOS sono chiusi.

Un MOS quando è acceso (stato ON) presenta una

resistenza di canale da frazioni di ohm fino a poche decine

di ohm, quando invece è chiuso ha una resistenza fino a un massimo di qualche centinaio

di megaohm, che in molte applicazioni si può considerare infinito.

L’interruttore è bilaterale perché l’ingresso e l’uscita sono intercambiabili.

I segnali d’ingresso possono essere digitali o analogici.

Questo componente viene utilizzato come porta logica, all’interno dei driver three-state,

nelle logiche dinamiche, nei flip-flop, nelle memorie.

Analogamente alla NAND e alla NOR, può essere considerata una porta universale perché

può realizzare qualunque tipo di funzione.

A lato è riportato il simbolo logico.

Nella precedente figura, è mostrato lo schema dell’interruttore

bilaterale.

Gating dei segnali digitali

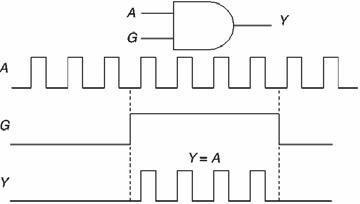

Le porte logiche possono essere adibite anche ad altre funzioni, quale ad esempio quella di

gating, ovvero al controllo del passaggio dei

segnali digitali posti all’ingresso.

Un esempio (funzione di gating della porta

AND) viene riportato in figura a lato;

sull’ingresso G è posto il segnale di controllo

mentre sulla linea A viene inviato il dato da

tra smettere all’uscita. Quando l’ingresso G

è a 1, il passaggio del segnale è abilitato

(Y = A), invece con G = 0 il passaggio è

disabilitato (Y = 0).

Funzione di gating della porta AND

(G = ingresso di gating).

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor