AD9910 Signal Generator

IZ5FCY

Quando perdi ridi, quando vinci sorridi.

Rumore di fase

Poiché il rumore di fase intrinseco del DDS è ovviamente inferiore a quello dei generatori PLL,

il valore finale dipende fortemente dalla sorgente di clock.

Per ottenere i valori indicati nella scheda tecnica dell'AD9910, durante la ri-progettazione della

mia shield Arduino DDS AD9910, mi sono attenuto rigorosamente a tutte le raccomandazioni di

Analog Devices:

layout del PCB a 4 strati, alimentazione separata di tutte e 4 le linee di alimentazione (3,3 V digitale,

3,3 V analogica, 1,8 V digitale e 1,8 V analogica).

Pertanto, quando si acquista una DDS AD9910 Arduino Shield, ci dobbiamo concentrare sui dati

della scheda tecnica dell'AD9910.

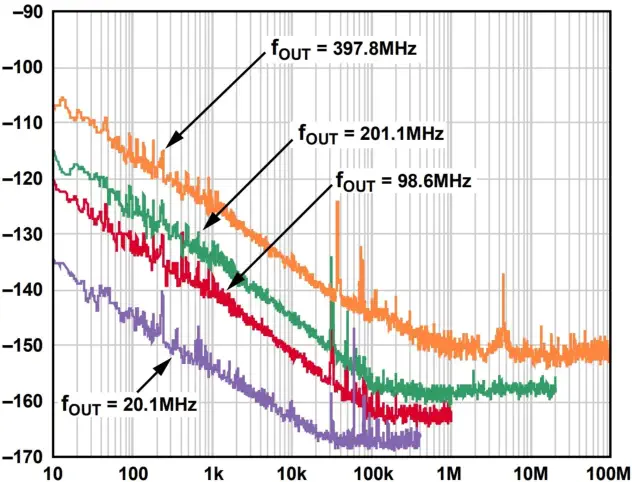

La seguente figura, mostra il livello di rumore quando si utilizza un clock di riferimento esterno da

1 GHZ, con il PLL disattivato.

Frequency offset (Hz)

AD9910 DDS Plot Phase Noise Residuale @ 1GHz con IL PLL disabilitato

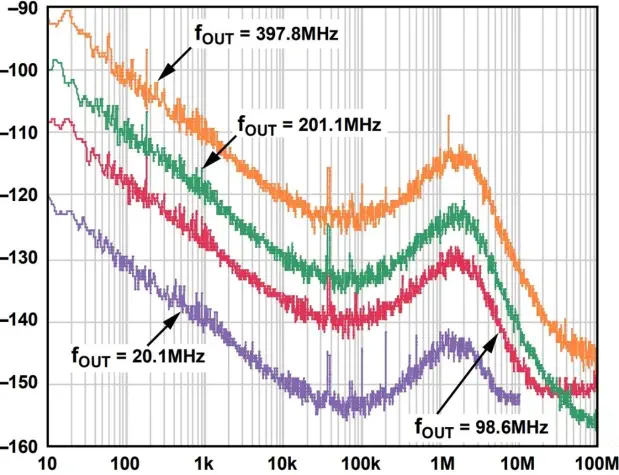

Frequency offset (Hz)

AD9910 DDS Plot Phase Noise Residuale in operazioni a 1GHz

utilizzando un Clock di Riferimento a 50MHz con 20xPLL Multiplier

Il diagramma mostra il livello di rumore quando si utilizza il PLL incorporato in DDS.

Il PLL moltiplica la frequenza di un generatore a 50 MHz per 20 volte.

Usiamo una frequenza simile - 40 MHz (moltiplicatore x25) o 50 MHz (moltiplicatore x20) di

TCXO che dà ancora più stabilità.

Confrontando questi due grafici, ad esempio, per Fout = 201,1 MHz e il PLL interno attivato a

10 kHz offset portante, il livello di rumore di fase è -130 dBc @ 10 kHz.

E con il PLL spento e utilizzando il clock esterno, il rumore di fase è di 145 dBc @ 10kHz.

Cioè, quando si utilizza un rumore di fase di clock esterno di 15 dBc migliore (inferiore).

Per la stessa frequenza Fout = 201,1 MHz e il PLL interno attivato a 1 MHz di offset portante, il

livello di rumore di fase è -124 dBc @ 1 MHz.

E con il PLL spento e utilizzando il clock esterno, il rumore di fase è di 158 dBc @ 1 MHz.

Cioè, quando si utilizza un rumore di fase di clock esterno di 34 dBc migliore (inferiore).

Conclusione: quando si utilizza il clock esterno, è possibile ottenere un rumore di fase molto più

basso rispetto all'utilizzo del PLL integrato. Ma non dimenticare che per ottenere tali risultati,

vengono richiesti maggiori requisiti al generatore esterno